# JML906x 10-MHz, RRIO, CMOS Operational Amplifiers

#### **Features**

• Rail-to-rail input and output

Low input offset voltage: ±0.4 mVUnity-gain bandwidth: 10 MHz

Low broadband noise: 14 nV/√Hz

Low input bias current: ±1 pA

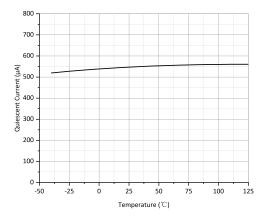

Low quiescent current: 740 μA(MAX)

Unity-gain stable

• Internal RFI and EMI filter

• Operational at supply voltages as low as 1.8 V

Easier to stabilize with higher capacitive load due to resistive open-loop output impedance

Shutdown version:JML906xS

• Internal RFI and EMI filter

• Extended temperature range: -40°C to 125°C

•compatibility AECQ-100

## **Applications**

E-bikes

· Smoke detectors

· HVAC: heating, ventilating, and air conditioning

• Refrigerators

• Motor control: AC induction

Refrigerators

Wearable devices

Laptop computers

· Washing machines

· Sensor signal conditioning

Power modules

• Barcode scanners

Active filters

· Low-side current sensing

#### **General Description**

JML9061 (single),JML9062 (dual), andJML9064 (quad) are single-, dual-, and quad- low-voltage (1.8V to 5.5 V) operational amplifiers (op amps) with rail to rail input and output-swing capabilities. These devices are highly cost-effective solutions for applications where low-voltage operation, a small footprint, and high capacitive load drive are required. Although the capacitive load drive of theJML906x is 100 pF, the resistive open-loop output impedance makes stabilizing with higher capacitive loads simpler.

XMO906xS devices include a shutdown mode that allow the amplifiers to switch into standby mode with typical current consumption less than 1  $\mu$ A.

JML906xS family helps simplify system design, because the family is unity-gain stable, integrates the RFI and EMI rejection filter, and provides no phase reversal in overdrive condition.

#### Device Information<sup>12</sup>

| PART NUMBER | PACKAGE    | BODY SIZE(NOM)    |

|-------------|------------|-------------------|

| JML9061     | SOT-23 (5) | 1.60 mm × 2.90 mm |

| 310125001   | SC70 (5)   | 1.25 mm × 2.00 mm |

| JML9061S    | SOT-23 (6) | 1.60 mm × 2.90 mm |

|             | SOIC (8)   | 3.91 mm × 4.90 mm |

| JML9062     | TSSOP (8)  | 3.00 mm × 4.40 mm |

| JIVIESOUZ   | VSSOP (8)  | 3.00 mm × 3.00 mm |

|             | WSON (8)   | 2.00 mm × 2.00 mm |

| JML9062S    | VSSOP (10) | 3.00 mm × 3.00 mm |

| JML9064     | SOIC (14)  | 8.65 mm × 3.91 mm |

| 310123004   | TSSOP (14) | 4.40 mm × 5.00 mm |

| JML9064S    | WQFN (16)  | 3.00 mm × 3.00 mm |

<sup>&</sup>lt;sup>1</sup> For all available packages, see the orderable addendum at the end of the data sheet.

Revision 1.0

<sup>&</sup>lt;sup>2</sup> Package is for preview only.

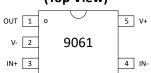

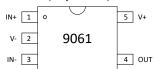

# Pin Configuration and Functions

# 5-Pin SOT-23 (Top View)

## 5-Pin SC70 (Top View)

#### Pin Functions:9061

|      | PIN    |      | I/O                  | DESCRIPTION                                                   |  |

|------|--------|------|----------------------|---------------------------------------------------------------|--|

| NAME | SOT-23 | SC70 | 1,0                  | DESCRIPTION                                                   |  |

| IN+  | 3      | 1    | I Noninverting input |                                                               |  |

| IN-  | 4      | 3    | I Inverting input    |                                                               |  |

| OUT  | 1      | 4    | 0                    | Out                                                           |  |

| V+   | 5      | 5    | _                    | Positive (highest) power supply                               |  |

| V-   | 2      | 2    | _                    | Negative (low) supply or ground (for single-supply operation) |  |

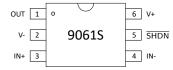

## 6-Pin SOT-23 (Top View)

#### Pin Functions:9061S

| PIN  |     | I/O               | DESCRIPTION                                                                                          |  |

|------|-----|-------------------|------------------------------------------------------------------------------------------------------|--|

| NAME | NO. | 1,0               | DESCRIPTION                                                                                          |  |

| IN+  | 3   | I                 | Noninverting input                                                                                   |  |

| IN-  | 4   | I Inverting input |                                                                                                      |  |

| OUT  | 1   | 0                 | Out                                                                                                  |  |

| SHDN | 5   | I                 | Shutdown: low = amp disabled, high = amp enabled. See Shutdown Function section for more information |  |

| V+   | 5   | _                 | Positive (highest) power supply                                                                      |  |

| V-   | 2   | _                 | Negative (low) supply or ground (for single-supply operation)                                        |  |

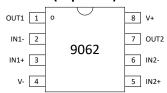

# 8-Pin SOIC, VSSOP, TSSOP (Top View)

# 8-Pin WSON With Exposed Thermal Pad (Top View)

#### Pin Functions: Pin Functions:9062

| PIN  |     | I/O | DESCRIPTION                                                   |  |

|------|-----|-----|---------------------------------------------------------------|--|

| NAME | NO. | 1,0 |                                                               |  |

| IN1- | 2   | I   | Inverting input, channel 1                                    |  |

| IN1+ | 3   | I   | Noninverting input, channel 1                                 |  |

| IN2- | 6   | I   | Inverting input, channel 2                                    |  |

| IN2+ | 5   | I   | Noninverting input, channel 2                                 |  |

| OUT1 | 1   | 0   | Output, channel 1                                             |  |

| OUT2 | 7   | 0   | Output, channel 2                                             |  |

| V+   | 8   | _   | Positive (highest) power supply                               |  |

| V-   | 4   | _   | Negative (low) supply or ground (for single-supply operation) |  |

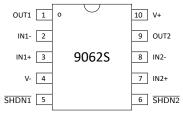

## 10-Pin VSSOP (Top View)

## Pin Functions: Pin Functions:9062S

| PIN   |     | I/O                             | DESCRIPTION                                                                                                    |

|-------|-----|---------------------------------|----------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | 1,0                             | DESCRIPTION                                                                                                    |

| IN1-  | 2   | I                               | Inverting input, channel 1                                                                                     |

| IN1+  | 3   | I                               | Noninverting input, channel 1                                                                                  |

| IN2-  | 8   | I                               | Inverting input, channel 2                                                                                     |

| IN2+  | 7   | I Noninverting input, channel 2 |                                                                                                                |

| OUT1  | 1   | 0                               | Output, channel 1                                                                                              |

| OUT2  | 9   | 0                               | Output, channel 2                                                                                              |

| SHDN1 | 5   | I                               | Shutdown: low = amp disabled, high = amp enabled.Channel 1. See Shutdown Function section for more information |

| SHDN2 | 6   | I                               | Shutdown: low = amp disabled, high = amp enabled.Channel 2. See Shutdown Function section for more information |

| V+    | 10  | _                               | Positive (highest) power supply                                                                                |

| V-    | 4   | _                               | Negative (low) supply or ground (for single-supply operation)                                                  |

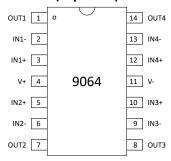

## 14-Pin SOIC, TSSOP (Top View)

#### Pin Functions: Pin Functions:9064

|      | PIN | I/O | DESCRIPTION                                                   |

|------|-----|-----|---------------------------------------------------------------|

| NAME | NO. | 1/0 | DESCRIPTION                                                   |

| IN1- | 2   | ı   | Inverting input, channel 1                                    |

| IN1+ | 3   | I   | Noninverting input, channel 1                                 |

| IN2- | 6   | ı   | Inverting input, channel 2                                    |

| IN2+ | 5   | ı   | Noninverting input, channel 2                                 |

| IN3- | 9   | ı   | Inverting input, channel 3                                    |

| IN3+ | 10  | ı   | Noninverting input, channel 3                                 |

| IN4- | 13  | ı   | Inverting input, channel 4                                    |

| IN4+ | 12  | ı   | Noninverting input, channel 4                                 |

| OUT1 | 1   | 0   | Output, channel 1                                             |

| OUT2 | 7   | 0   | Output, channel 2                                             |

| OUT3 | 8   | 0   | Output, channel 3                                             |

| OUT4 | 14  | 0   | Output, channel 4                                             |

| V+   | 4   | _   | Positive (highest) power supply                               |

| V-   | 11  | _   | Negative (low) supply or ground (for single-supply operation) |

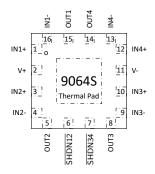

# 16-Pin WQFN With Exposed Thermal Pad (Top View)

#### **Pin Functions: Pin Functions:9064S**

|        | PIN | 1/0 | DESCRIPTION                                                                                                      |

|--------|-----|-----|------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | I/O | DESCRIPTION                                                                                                      |

| IN1-   | 16  | 1   | Inverting input, channel 1                                                                                       |

| IN1+   | 1   | 1   | Noninverting input, channel 1                                                                                    |

| IN2-   | 4   | 1   | Inverting input, channel 2                                                                                       |

| IN2+   | 3   | 1   | Noninverting input, channel 2                                                                                    |

| IN3-   | 9   | 1   | Inverting input, channel 3                                                                                       |

| IN3+   | 10  | 1   | Noninverting input, channel 3                                                                                    |

| IN4-   | 13  | 1   | Inverting input, channel 4                                                                                       |

| IN4+   | 12  | 1   | Noninverting input, channel 4                                                                                    |

| OUT1   | 15  | 0   | Output, channel 1                                                                                                |

| OUT2   | 5   | 0   | Output, channel 2                                                                                                |

| OUT3   | 8   | 0   | Output, channel 3                                                                                                |

| OUT4   | 14  | 0   | Output, channel 4                                                                                                |

| SHDN12 | 5   | ı   | Shutdown: low = amp disabled, high = amp enabled.Channel 1,2. See Shutdown Function section for more information |

| SHDN34 | 7   | ı   | Shutdown: low = amp disabled, high = amp enabled.Channel 3,4. See Shutdown Function section for more information |

| V+     | 2   | _   | Positive (highest) power supply                                                                                  |

| V-     | 11  | _   | Negative (low) supply or ground (for single-supply operation)                                                    |

# **Specifications**

#### **Absolute Maximum Ratings**

Over operating ambient temperature (unless otherwise noted)<sup>1</sup>

|                                      |                           |              | MIN        | MAX               | UNIT |

|--------------------------------------|---------------------------|--------------|------------|-------------------|------|

| Supply voltage [(V+)                 | - (V-)]                   |              | 0          | 6                 | V    |

|                                      | Voltage                   | Common-mode  | (V-) - 0.5 | (V+) + 0.5        | V    |

| Signal input pins                    | Voitage                   | Differential |            | (V+) - (V-) + 0.2 | V    |

|                                      | Current <sup>2</sup>      | ·            | -1         | 10                | mA   |

| Output short-circuit <sup>3</sup>    |                           |              | Conti      | nuous             | mA   |

|                                      | Specified, T <sub>A</sub> |              | -40        | 125               |      |

| Temperature Junction, T <sub>J</sub> | Junction, T <sub>J</sub>  |              |            | 150               | °C   |

|                                      | Storage, T <sub>stg</sub> |              | -65        | 150               |      |

<sup>&</sup>lt;sup>1</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **ESD Ratings**

|                                          |                                                                              | VALUE | UNIT |

|------------------------------------------|------------------------------------------------------------------------------|-------|------|

| 9061 PACKAGES                            |                                                                              |       |      |

| V <sub>ESD</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>1</sup>              | ±2500 | V    |

| VESD Electrostatic discharge             | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>1</sup> |       |      |

| ALL OTHER PACKAGES                       |                                                                              |       |      |

| V Flootrostatic discharge                | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>1</sup>              |       | V    |

| V <sub>ESD</sub> Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>1</sup> | ±1500 | V    |

$<sup>^{\,1}\,</sup>$  JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process

#### **Recommended Operating Conditions**

Over operating ambient temperature (unless otherwise noted)

|                      |                                                              | MIN        | MAX        | UNIT |

|----------------------|--------------------------------------------------------------|------------|------------|------|

| Vs                   | Supply voltage $(V_S = [V+] - [V-])$                         | 1.8        | 5.5        | V    |

| VI                   | Input voltage range                                          | (V-) - 0.1 | (V+) + 0.1 | V    |

| Vo                   | Output voltage range                                         | V-         | V+         | V    |

| V <sub>SHDN_IH</sub> | High level input voltage at shutdown pin (amplifier enabled) | 1.2        | V+         | V    |

| V <sub>SHDN_IL</sub> | Low level input voltage at shutdown pin (amplifier disabled) | V-         | 0.2        | V    |

| T <sub>A</sub>       | Specified temperature                                        | -40        | 125        | °C   |

<sup>&</sup>lt;sup>2</sup> Input pins are diode-clamped to the power-supply rails. Current limit input signals that can swing more than 0.5 V beyond the supply rails to 10 mA or less.

$<sup>^{\</sup>rm 3}\,$  Short-circuit to ground, one amplifier per package.

$<sup>^{2}\,</sup>$  JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **Electrical Characteristics**

For  $V_S$  (Total Supply Voltage) = (V+) – (V–) = 1.8V to 5.5V at  $T_A$  = 25°C,  $R_L$  = 10k $\Omega$  connected to  $V_S$  / 2,  $V_{CM}$  =  $V_S$  / 2, and  $V_{OUT}$  =  $V_S$  / 2 (unless otherwise noted)

| PARAME               | TER                                | TEST CONDITIONS                                                                                                                 | MIN        | TYP  | MAX        | UNIT   |

|----------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------|------|------------|--------|

| OFFSET '             | VOLTAGE                            |                                                                                                                                 |            |      |            |        |

| V <sub>OS</sub>      | input offset voltage               | V <sub>os</sub> =5V                                                                                                             |            | ±0.4 | ±1.6       | mV     |

| VOS                  | input onset voitage                | V <sub>S</sub> = 5 V, T <sub>A</sub> = -40°C to 125°C                                                                           |            |      | ±1.8       | IIIV   |

| dV <sub>os</sub> /dT | Drift                              | $V_S = 5 \text{ V}, T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$                                                          |            | ±0.5 |            | μV/°C  |

| PSRR                 | Power-supply rejection ratio       | $V_S = 1.8 \text{ V} - 5.5 \text{ V}, V_{CM} = (V-)$                                                                            |            | ±7   | ±100       | μV/V   |

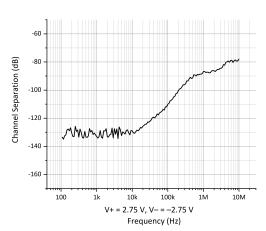

|                      | Channel separation, DC             | At DC                                                                                                                           |            | 134  | 140        | dB     |

| INPUT V              | OLTAGE RANGE                       |                                                                                                                                 |            |      |            |        |

| V <sub>CM</sub>      | Common-mode voltage range          | VS = 1.8 V to 5.5 V                                                                                                             | (V-) - 0.1 |      | (V+) + 0.1 | V      |

|                      |                                    | $V_S = 5.5 \text{ V, (V-)} - 0.1 \text{ V} < V_{CM} < (V+) - 1.5 \text{ V, } T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ | 86         | 104  |            |        |

| CMDD                 |                                    | V <sub>S</sub> = 5.5 V, - 0.1 V < V <sub>CM</sub> < 5.6<br>V, T <sub>A</sub> = -40°C to 125°C                                   | 60         | 87   |            | dB     |

| CMRR                 | Common-mode rejection ratio        | $V_S = 1.8 \text{ V, (V-)} - 0.1 \text{ V} < V_{CM} < (V+) - 1.5 \text{ V, } T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ | 88         | 108  |            | -      |

|                      |                                    | V <sub>S</sub> = 1.8 V, -0.1 V < V <sub>CM</sub> < 1.9<br>V, T <sub>A</sub> = -40°C to 125°C                                    |            | 88   |            |        |

| INPUT B              | IAS CURRENT                        |                                                                                                                                 |            |      |            |        |

| I <sub>B</sub>       | Input bias current                 |                                                                                                                                 |            | ±1   |            | рА     |

| I <sub>OS</sub>      | Input offset current               |                                                                                                                                 |            | ±0.3 |            | рА     |

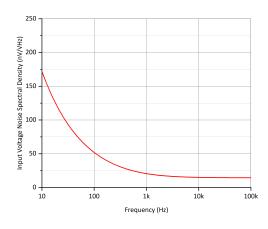

| NOISE                |                                    |                                                                                                                                 |            |      |            |        |

| E <sub>n</sub>       | Input voltage noise (peak to peak) |                                                                                                                                 |            | 5.7  |            | μVpp   |

| _                    | Innuitualte de desertos            | VS = 5 V, f = 10 kHz                                                                                                            |            | 15   |            |        |

| e <sub>n</sub>       | Input voltage noise density        | VS = 5 V, f = 1 kHz                                                                                                             |            | 20   |            | nV/√Hz |

| i <sub>n</sub>       | Input current noise density        | f= 1 kHz                                                                                                                        |            | 4    |            | fA/√Hz |

| INPUT C              | APACITANCE                         |                                                                                                                                 |            |      |            |        |

| C <sub>ID</sub>      | Differential                       |                                                                                                                                 |            | 1.2  |            | pF     |

| C <sub>IC</sub>      | Common-mode                        |                                                                                                                                 |            | 2.4  |            | pF     |

| OPEN-LO              | OOP GAIN                           |                                                                                                                                 |            |      |            | ı      |

|                      |                                    | $V_S$ = 1.8 V, , (V–) + 0.04 V < $V_O$ < (V+) – 0.04 V, $R_L$ = 10k $\Omega$                                                    | 103        | 128  |            |        |

| ۸                    | Open loop voltage gain             | $V_S$ = 5.5 V, , (V–) + 0.05 V < $V_O$ < (V+) – 0.05 V, $R_L$ = 10k $\Omega$                                                    | 111        | 135  |            | - 10   |

| A <sub>OL</sub>      | Open-loop voltage gain             | $V_S$ = 1.8 V, , (V–) + 0.06 V < $V_O$ < (V+) – 0.06 V, $R_L$ = 2k $\Omega$                                                     |            | 127  |            | dB     |

|                      |                                    | $V_S$ = 5.5 V, , (V–) + 0.15 V < $V_O$ < (V+) – 0.15 V, $R_L$ = 2k $\Omega$                                                     |            | 130  |            |        |

## **Electrical Characteristics (continued)**

For  $V_S$  (Total Supply Voltage) = (V+) – (V–) = 1.8V to 5.5V at  $T_A$  = 25°C,  $R_L$  = 10k $\Omega$  connected to  $V_S$  / 2,  $V_{CM}$  =  $V_S$  / 2, and  $V_{OUT}$  =  $V_S$  / 2 (unless otherwise noted)

| PARAME          | ETER                                           | TEST CONDITIONS                                                                                | MIN | TYP      | MAX | UNIT |

|-----------------|------------------------------------------------|------------------------------------------------------------------------------------------------|-----|----------|-----|------|

| FREQUE          | NCY RESPONSE                                   |                                                                                                |     |          |     |      |

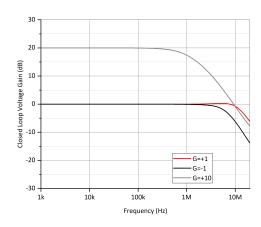

| GBW             | Gain bandwidth product                         | V <sub>S</sub> = 5 V, G = +1                                                                   |     | 10       |     | MHz  |

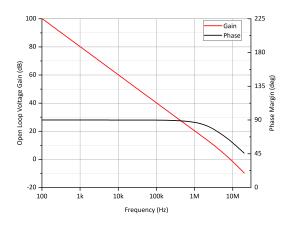

| $\varphi_{m}$   | Phase margin                                   | V <sub>S</sub> = 5 V, G = +1                                                                   |     | 64       |     | 0    |

| SR              | Slew rate                                      | V <sub>S</sub> = 5 V, G = +1                                                                   |     | 7        |     | V/µs |

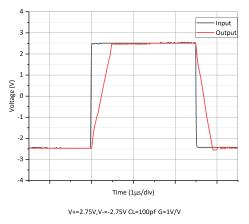

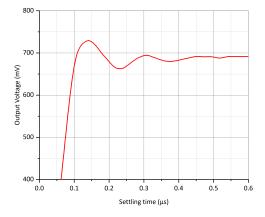

| t <sub>S</sub>  | Settling time                                  | To 0.1%, V <sub>S</sub> = 5 V, 2-V step , G = +1, C <sub>L</sub> = 100 pF                      |     | 0.5      |     | μs   |

|                 |                                                | To 0.01%, V <sub>S</sub> = 5 V, 2-V step , G<br>= +1, C <sub>L</sub> = 100 pF                  |     | 0.9      |     |      |

| t <sub>or</sub> | Overload recovery time                         | $V_S = 5.5 \text{ V, } V_{IN}^* \text{ gain } > V_S$                                           |     | 0.6      |     | μs   |

| THD+N           | Total harmonic distortion + noise <sup>1</sup> | $V_S = 5.5 \text{ V}, V_{CM} = 2.5 \text{ V}, V_O = 1$<br>$V_{RMS}, G = +1, f = 1 \text{ kHz}$ |     | 0.00047% |     |      |

| ОИТРИТ          | T                                              |                                                                                                |     |          |     |      |

| Vo              | Output swing from supply rails                 | $V_S = 5.5 \text{ V,R}_L = 10 \text{ k}\Omega$                                                 |     |          | 6   | mV   |

| v <sub>O</sub>  | Output swing from supply rails                 | $V_{O} = 5.5 \text{ V,R}_{L} = 2 \text{ k}\Omega$                                              |     |          | 20  | IIIV |

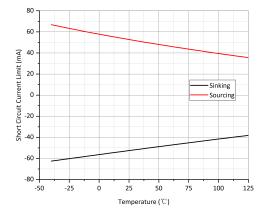

| I <sub>SC</sub> | Short-circuit current                          | V <sub>S</sub> = 5 V                                                                           |     | ±55      |     | mA   |

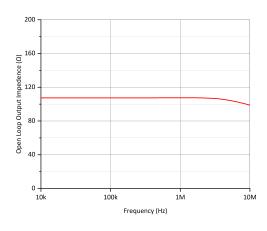

| Z <sub>O</sub>  | Open-loop output impedance                     | V <sub>S</sub> = 5 V, f = 10 MHz                                                               |     | 100      |     | Ω    |

| POWER           | SUPPLY                                         |                                                                                                |     |          |     |      |

| 1.              | Quiescent current per amplifier                | V <sub>S</sub> = 5.5 V,I <sub>O</sub> = 0mA                                                    |     | 554      | 710 | uA   |

| IQ              | Quiescent current per amplifier                | $V_S = 5.5 \text{ V,I}_O = 0\text{mA,T}_A = -40^{\circ}\text{C}$<br>to 125°C                   |     |          | 740 | - uA |

$<sup>^{1}</sup>$  Third-order filter; bandwidth = 80 kHz at -3 dB.

#### **Typical Characteristics**

at  $T_A$  = 25°C,  $V_S$  = 5.5 V,  $R_L$  = 10 k $\Omega$  connected to  $V_S$  / 2,  $V_{CM}$  =  $V_S$  / 2, and  $V_{OUT}$  =  $V_S$  / 2 (unless otherwise noted)

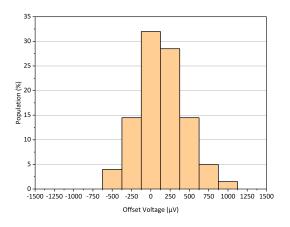

Figure 1: Offset Voltage Production Distribution

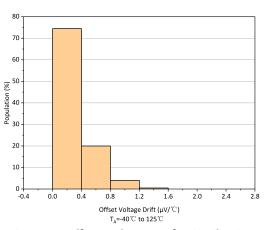

Figure 2: Offset Voltage Drift Distribution

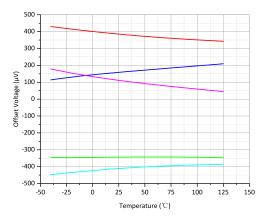

Figure 3: Offset Voltage vs Temperature

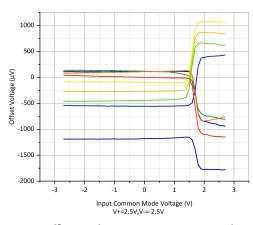

Figure 4: Offset Voltage vs Common-Mode Voltage

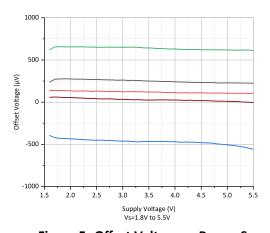

Figure 5: Offset Voltage vs Power Supply

Figure 6: Open-Loop Gain and Phase vs Frequency

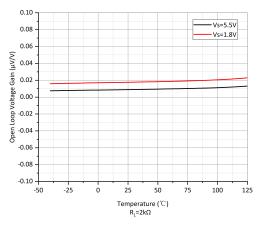

For  $V_S$ (Total Supply Voltage) = (V+) – (V–) = 1.8V to 5.5V at  $T_A$  = 25°C,  $R_L$  = 10k $\Omega$  connected to  $V_S$  / 2,  $V_{CM}$  =  $V_S$  / 2, and  $V_{OUT}$  =  $V_S$  / 2 (unless otherwise noted)

Figure 7: Open-Loop Gain vs Temperature

Figure 8: Closed-Loop Gain vs Frequency

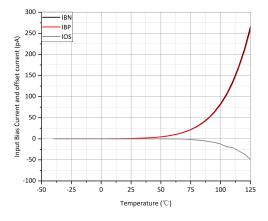

Figure 9: Input Bias Current vs Temperature

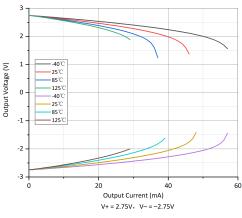

Figure 10: Output Voltage Swing vs Output Current

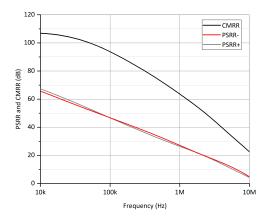

Figure 11: Offset CMRR and PSRR vs Frequency

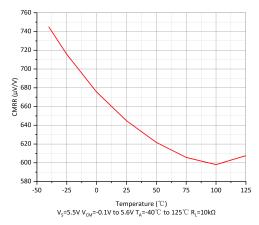

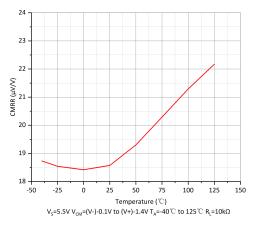

Figure 12: CMRR vs Temperature

For  $V_S$  (Total Supply Voltage) = (V+) – (V–) = 1.8V to 5.5V at  $T_A$  = 25°C,  $R_L$  = 10k $\Omega$  connected to  $V_S$  / 2,  $V_{CM}$  =  $V_S$  / 2, and  $V_{OUT}$  =  $V_S$  / 2 (unless otherwise noted)

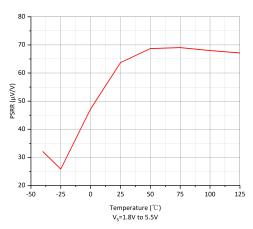

Figure 13: CMRR vs Temperature

Figure 14: PSRR vs Temperature

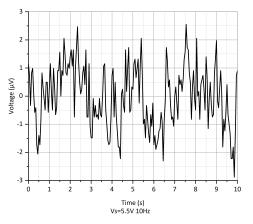

Figure 15: 0.1-Hz to 10-Hz Input Voltage Noise

Figure 16: Input Voltage Noise Spectral Density vs Frequency

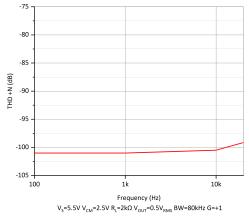

Figure 17: THD + N vs Frequency

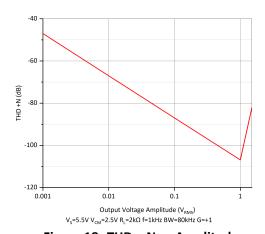

Figure 18: THD + N vs Amplitude

For  $V_S$  (Total Supply Voltage) = (V+) – (V–) = 1.8V to 5.5V at  $T_A$  = 25°C,  $R_L$  = 10k $\Omega$  connected to  $V_S$  / 2,  $V_{CM}$  =  $V_S$  / 2, and  $V_{OUT} = V_S / 2$  (unless otherwise noted)

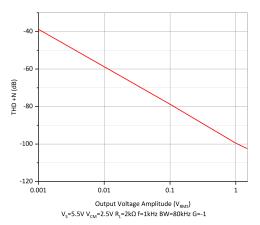

Figure 19: THD + N vs Amplitude

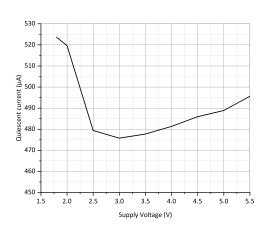

Figure 20: Quiescent Current vs Supply Voltage

Figure 21: Quiescent Current vs Temperature

Figure 22: Open-Loop Output Impedance vs Frequency

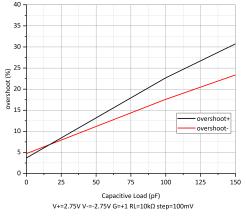

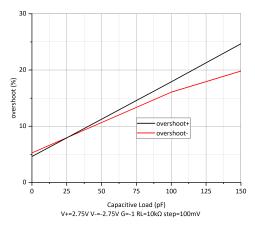

Figure 23: Small-Signal Overshoot vs Load Capacitance Figure 24: Small-Signal Overshoot vs Load Capacitance

For  $V_S$ (Total Supply Voltage) = (V+) – (V–) = 1.8V to 5.5V at  $T_A$  = 25°C,  $R_L$  = 10k $\Omega$  connected to  $V_S$  / 2,  $V_{CM}$  =  $V_S$  / 2, and  $V_{OUT}$  =  $V_S$  / 2 (unless otherwise noted)

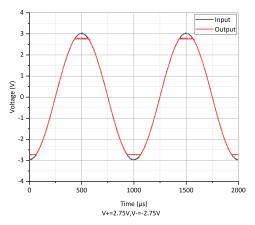

Figure 25: No Phase Reversal

Figure 26: Overload Recovery

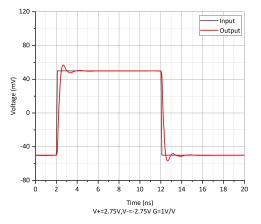

Figure 27: Small-Signal Step Response

Figure 28: Large-Signal Step Response

Figure 29: Short-Circuit Current vs Temperature

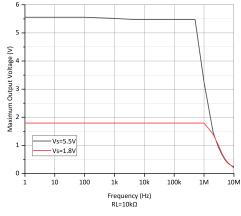

Figure 30: Maximum Output Voltage vs Frequency and Supply Voltage

For  $V_S$ (Total Supply Voltage) = (V+) – (V–) = 1.8V to 5.5V at  $T_A$  = 25°C,  $R_L$  = 10k $\Omega$  connected to  $V_S$  / 2,  $V_{CM}$  =  $V_S$  / 2, and  $V_{OUT}$  =  $V_S$  / 2 (unless otherwise noted)

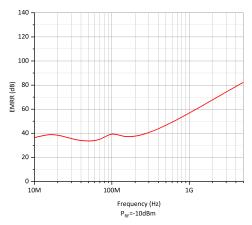

Figure 31: Electromagnetic Interference Rejection Ratio Referred to Noninverting Input (EMIRR+) vs Frequency

Figure 32: Channel Separation vs Frequency

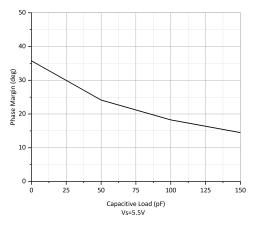

Figure 33: Phase Margin vs Capacitive Load

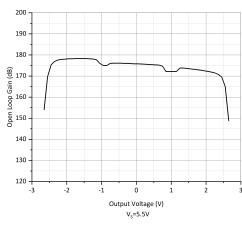

Figure 34: Open Loop Voltage Gain vs Output Voltage

Figure 35: Large Signal Settling Time (Positive)

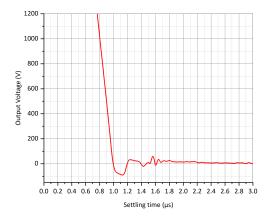

Figure 36: Large Signal Settling Time (Negative)

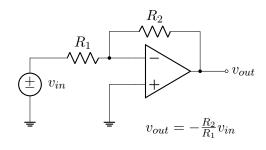

## **Typical Application**

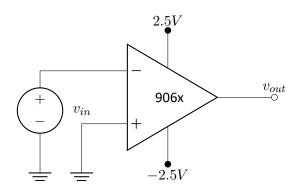

#### **Comparators**

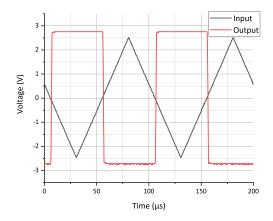

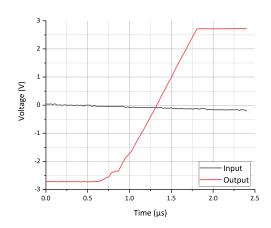

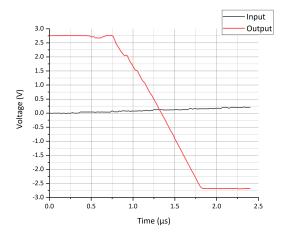

Comparators are used to differentiate between two different signal levels. For example, a comparator can be used to differentiate between an overvoltage situation and normal operation. The XMO906x can be used as comparators by applying the two voltages being compared to each input without any feedback from output to inverting input. The XMO906x features a rail-to-rail input and output stage with an input common-mode range that exceeds the supply rails by 100 mV. The XMO906x is designed to prevent phase reversal over the entire input common-mode range. The propagation delay for the XMO906x used as a comparator is equal to the overload recovery time plus the slew rate. Overdrive voltages less than 100 mV result in longer propagation delays because the overload recovery time increases and the slew rate decreases.

#### **Design Requirements**

The design requirements for this design are:

Supply voltage: ±2.5 V

Input (VIN): -2.5 V to 2.5 V

Threshold voltage (VTH): 0 V

#### **Detailed Design Procedure**

The inverting comparator circuit applies the input voltage (VIN) to the inverting terminal of the op amp and ground to to the non-inverting terminal of the op amp as threshold voltage. The circuit is shown in following figure. When VIN is less then VTH, the output voltage transitions to the positive supply and equals the high-level output voltage. When VIN is greater than VTH, the output voltage transitions to the negative supply and equals the low-level output voltage.

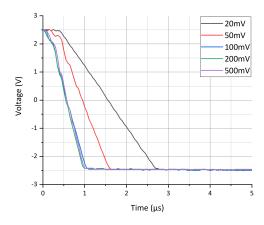

#### **Application Curves**

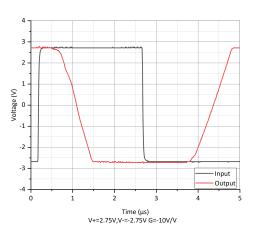

Figure 37: Comparator Response to Input Voltage (Propagation Delay Included)

Figure 38: Rising Edge

Figure 39: Falling Edge

Figure 40: Falling Edge Propagation Delay vsInput

Overdrive Voltage

# Packaging Infromation

| Orderable<br>Device | Status | Package<br>Type | Pins | Package<br>Qty | Eco Plan   | Op<br>Temp(°C) | Marking |

|---------------------|--------|-----------------|------|----------------|------------|----------------|---------|

| JML9061IDBVR        | ACTIVE | SOT-23          | 5    | 4000           | RoHS Green | -40 to 125     | 15      |

| JML9062IDGKR        | ACTIVE | MSOP            | 8    | 4000           | RoHS Green | -40 to 125     | 2M      |

| JML9062IDR          | ACTIVE | SOP             | 8    | 4000           | RoHS Green | -40 to 125     | 25      |

| JML9064IDR          | ACTIVE | SOP             | 14   | 2500           | RoHS Green | -40 to 125     | 45      |

| JML9064IPWR         | ACTIVE | TSSOP           | 14   | 2500           | RoHS Green | -40 to 125     | 4T      |

# **Package Outline Dimension**

#### SOT23-5

- 1.All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only.

- 2. This drawing is subject to change without notice.

- 3.Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 4. Support pin may differ or may not be present.

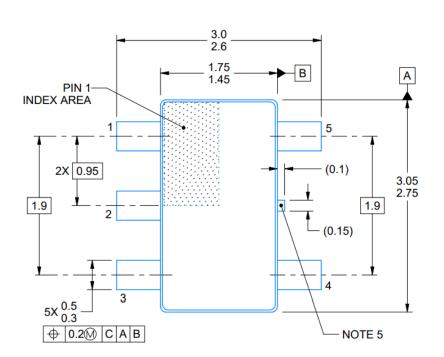

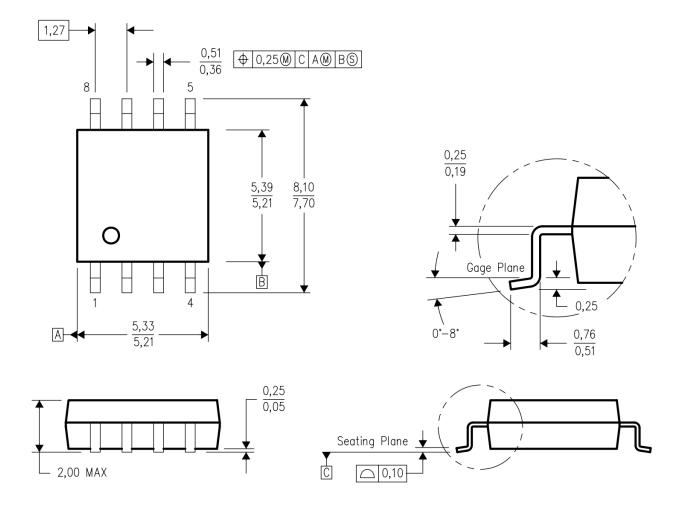

#### SOP8

- 1.All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only.

- 2. This drawing is subject to change without notice.

- 3.Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 4. Support pin may differ or may not be present.

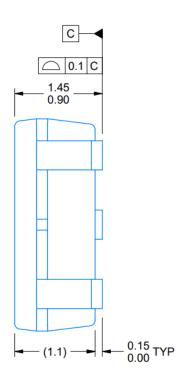

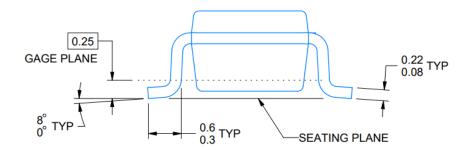

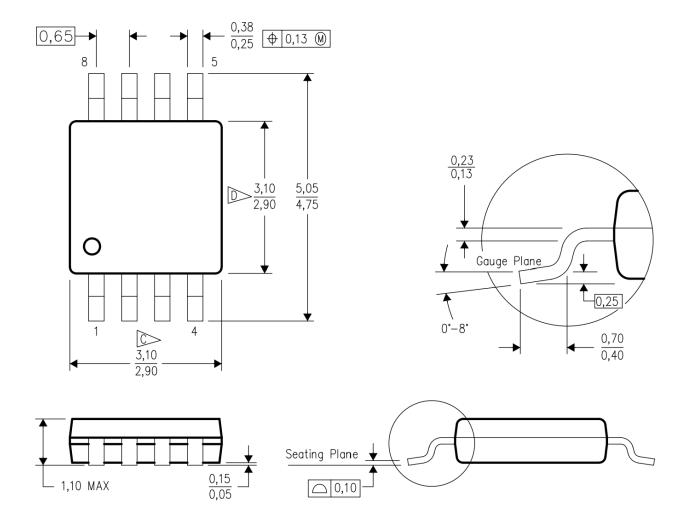

#### MSOP8

- 1.All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only.

- 2. This drawing is subject to change without notice.

- 3.Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 4. Support pin may differ or may not be present.

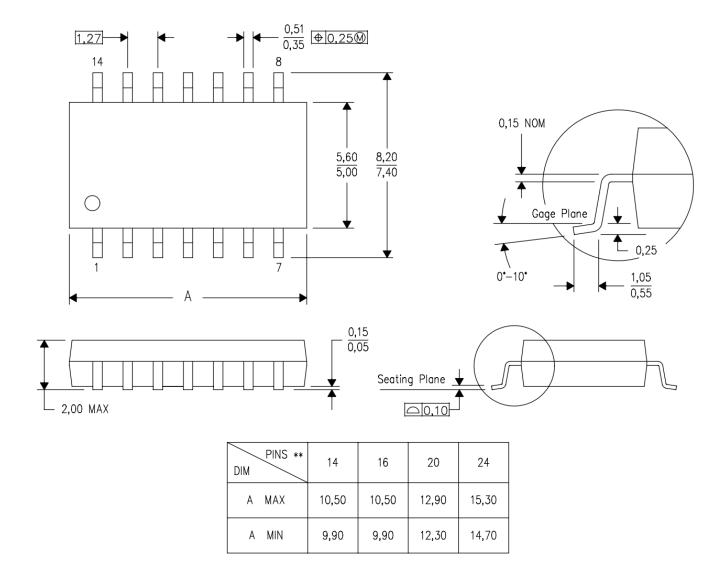

#### SOP14

- 1.All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only.

- 2. This drawing is subject to change without notice.

- 3.Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 4. Support pin may differ or may not be present.

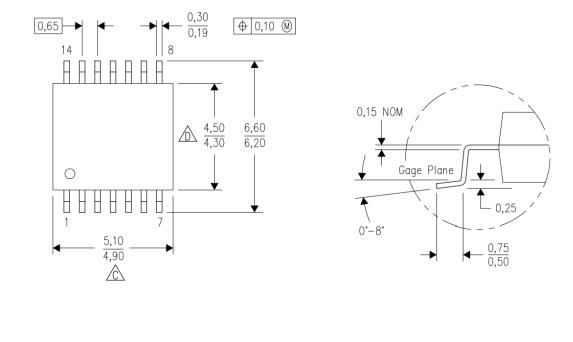

#### TSSOP14

#### NOTE:

1.All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only.

$\frac{0,15}{0,05}$

2. This drawing is subject to change without notice.

1,20 MAX

3.Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

Seating Plane

0,10

4. Support pin may differ or may not be present.